연산 증폭기? 매우 간단합니다! 연산 증폭기 반전 증폭기. 작동 원리

반전 증폭기는 가장 간단하고 가장 일반적으로 사용되는 아날로그 회로 중 하나입니다. 두 개의 저항만으로 필요한 이득을 설정할 수 있습니다. 계수를 1보다 작게 만들어 입력 신호를 약화시키는 것을 막는 것은 없습니다.

종종 다른 R3이 회로에 추가되며 저항은 R1과 R2의 합과 같습니다.

반전 증폭기의 작동 방식을 이해하기 위해 간단한 회로를 시뮬레이션해 보겠습니다. 입력에서 4V의 전압이 있고 저항의 저항은 R1 \u003d 1k 및 R2 \u003d 2k입니다. 물론 이 모든 것을 공식에 대입하고 결과를 즉시 계산할 수도 있지만 이 계획이 정확히 어떻게 작동하는지 봅시다.

연산 증폭기의 기본 작동 원리를 상기시켜 보겠습니다.

규칙 #1 - 연산 증폭기출력은 OOS(음의 피드백)를 통한 입력에 영향을 미치므로 반전(-) 및 비반전(+) 입력 모두에서 두 입력의 전압이 동일해집니다.

비 반전 입력 (+)은 접지에 연결되어 있습니다. 즉, 전압은 0V입니다. 규칙 #1에 따라 반전 입력(-)도 0V여야 합니다.

따라서 저항 R1의 단자에서의 전압과 저항 1k를 알고 있습니다. 따라서 도움을 받아 계산을 수행하고 저항 R1을 통해 흐르는 전류의 양을 계산할 수 있습니다.

IR1 \u003d UR1 / R1 \u003d (4V-0V) / 1k \u003d 4mA.

규칙 #2 - 증폭기 입력은 전류를 끌어오지 않는다

따라서 R1을 통해 흐르는 전류는 R2를 통해 더 흐릅니다!

다시 옴의 법칙을 사용하여 저항 R2에서 발생하는 전압 강하를 계산합니다. 우리는 저항을 알고 그것을 통과하는 전류를 알고 있으므로 다음을 수행합니다.

UR2 = IR2R2 = 4mA *2k = 8V.

출력에 8V가 있다는 것이 밝혀졌습니다. 확실히 그런 방식은 아닙니다. 이것이 반전 증폭기라는 것을 상기시켜 드리겠습니다. 즉, 입력에 양의 전압을 적용하고 출력에서 음의 전압을 제거하는 경우입니다. 어떻게 됩니까?

이는 피드백이 반전 입력(-)에서 설정되고 입력에서 전압을 균등화하기 위해 증폭기가 출력에서 전위를 감소시키기 때문입니다. 저항 연결은 간단한 것으로 간주될 수 있으므로 연결 지점의 전위가 0이 되려면 출력이 마이너스 8볼트(Uout)여야 합니다. = -(R2/R1)*Uin.

세 번째 규칙과 관련된 또 다른 catch가 있습니다.

규칙 번호 3 - 입력 및 출력의 전압은 연산 증폭기의 양과 음 공급 전압 사이의 범위에 있어야 합니다.

즉, 우리가 계산한 전압이 실제로 증폭기를 통해 얻을 수 있는지 확인해야 합니다. 종종 초보자는 증폭기가 자유 에너지의 원천으로 작동하고 무에서 전압을 생성한다고 생각합니다. 그러나 증폭기가 작동하려면 전력도 필요하다는 것을 기억해야 합니다.

클래식 증폭기는 -15V 및 +15V의 전압에서 작동합니다. 이러한 상황에서 우리가 계산한 -8V는 이 범위에 있기 때문에 실제 전압입니다.

그러나 최신 증폭기는 종종 5V 이하에서 작동합니다. 이러한 상황에서 증폭기가 출력에서 마이너스 8V를 줄 가능성은 없습니다. 그러므로 회로를 설계할 때 이론적인 계산은 항상 현실과 물리적 능력에 의해 뒷받침되어야 한다는 것을 항상 기억하십시오.

반전 증폭기에는 한 가지 단점이 있습니다. 증폭기 입력은 저항이 매우 높고 전류를 거의 소비하지 않아 대부분의 경우 무시할 수 있기 때문에 신호 소스를 로드하지 않는다는 것을 이미 알고 있습니다(규칙 #2).

반전 증폭기는 저항 R1의 저항과 동일한 입력 임피던스를 가지며 실제로 범위는 1k ... 1M입니다. 비교를 위해 전계 효과 트랜지스터 입력이 있는 증폭기의 저항은 수백 메가옴, 심지어는 기가옴 정도입니다! 따라서 때때로 증폭기 앞에 전압 팔로워를 설치하는 것이 좋습니다.

좋은 날. 지난 기사에서 나는 영양에 대해 이야기했습니다. 이 기사에서는 사용에 대해 이야기 할 것입니다. 선형 회로의 연산 증폭기.

전압 팔로워

내가 이야기 할 첫 번째 회로는 단위 이득 증폭기 회로 (단위 증폭기) 또는 소위입니다. 이 증폭기의 회로는 아래와 같습니다.

유니티 이득 증폭기(전압 팔로워).

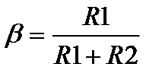

이 회로는 수정 사항이며 차이점은 반전 입력에 피드백 저항과 저항이 없다는 것입니다. 따라서 연산증폭기의 출력전압은 연산증폭기의 반전입력에 완전히 공급되고, 결과적으로 피드백 전달계수는 1(β=1)이 된다.

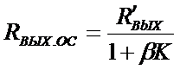

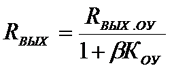

아시다시피 피드백이 있는 연산 증폭기의 입력 임피던스는 다음 식에 의해 결정됩니다.

![]()

- 여기서 R BX는 OS가 없는 OS의 입력 임피던스이고,

그런 다음 전압 팔로워의 경우 입력 저항은 다음과 같습니다.

피드백 연산 증폭기의 출력 임피던스는 다음 식입니다.

- 여기서 R BYX는 OS가 없는 OS의 입력 임피던스이고,

- β는 OS 회로의 전송 계수,

- K는 OS가 없는 OS의 이득입니다.

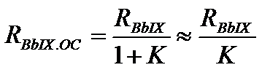

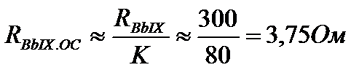

전압 팔로워는 피드백 전달 계수가 1(β = 1)이므로 출력 저항은 다음 형식을 갖습니다.

전압 팔로워의 매개변수 계산 예

예를 들어, 필요한 주파수, 입력 임피던스 R BX = 500kOhm, 출력 임피던스 R BYX = 300Ohm에서 K U = 80(38dB)의 이득을 갖는 연산 증폭기의 전압 팔로워를 계산해 보겠습니다.

입력 임피던스전압 추종자는

전압 팔로워의 출력 임피던스는

가장 단순한 전압 팔로워 회로의 단점

개방 회로 OS가있는 연산 증폭기의 이득이 주파수에 따라 변하기 때문에 (주파수가 증가하면 이득이 감소함) 따라서 입력 및 출력 저항도 주파수에 의존합니다 (주파수가 증가하면 입력 저항이 감소합니다 , 출력 저항이 증가합니다).

입력 신호에 충분히 큰 DC 성분과 상당한 진폭 스윙이 있는 경우 공통 모드 입력 전압의 한계를 초과하는 상황이 발생할 수 있습니다. 이 문제를 해결하기 위해서는 비반전 입력에 디커플링 커패시터를 통해 신호를 인가해야 하며, 비반전 입력과 접지 사이에 저항을 연결해야 하는데, 이 저항이 중계기의 입력 저항에 영향을 미치게 된다.

연산 증폭기 제조업체에서 권장하는 전압 팔로어의 매개변수를 개선하는 또 다른 방법은 OS 회로와 비반전 입력과 "접지" 사이에 동일한 저항을 갖는 저항을 포함하는 것입니다. 이 경우 연산 증폭기의 이득도 1과 같지만 입력 및 출력 저항은 연산 증폭기의 매개변수가 아닌 외부 저항에 따라 달라집니다.

단일 증폭기의 매개변수를 개선하는 가장 효과적인 방법은 전압 팔로워 회로 이후에 큰 출력 전류를 제공하는 전력 증폭기를 켜는 회로입니다. 이 경우 전압 이득은 대략 1이 되며 피드백 전류는 전력 증폭기의 특성에 의해 결정됩니다(입력 및 출력 저항에 두 증폭기의 이득이 곱해짐).

비 반전 증폭기

실제로 이득이 1인 비반전 증폭기인 전압 팔로워를 분석한 후 임의 이득을 갖는 비반전 증폭기 회로를 고려해보자. 이 유형의 증폭기는 입력 임피던스가 높고 출력 임피던스가 낮다는 특징이 있으며 증폭기 회로는 아래와 같습니다.

![]()

비 반전 증폭기의 개략도.

이 회로는 연산 증폭기를 켜기 위한 표준 회로 중 하나이며 연산 증폭기 DA1, 바이어스 저항 R1 및 피드백 저항 R2를 포함합니다. 이 회로의 연산 증폭기는 직렬 전압 피드백으로 덮여 있으며 피드백 회로의 이득은 다음과 같습니다.

그러면 비 반전 증폭기의 입력 임피던스는

R BX.OU - 개방형 OS 회로가 있는 OS의 입력 임피던스,

TO OU - 개방형 OS 회로가 있는 연산 증폭기의 이득 계수.

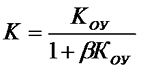

비반전 증폭기의 출력 임피던스는 다음 식으로 계산할 수 있습니다.

R OUTPUT OU - 개방형 OS 회로가 있는 OU의 출력 임피던스.

비 반전 증폭기 이득

이 유형의 증폭기에는 입력에 일정 수준의 바이어스 전압 UCM이 있으므로 이 회로는 입력의 바이어스 전압 수준이 큰 영향을 미치지 않는 경우에 적용할 수 있습니다. 입력의 바이어스 전압 레벨은

![]()

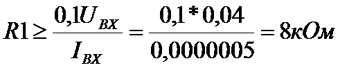

비 반전 증폭기 계산의 예

K = 10의 이득을 제공해야 하는 비반전 증폭기를 계산합니다. 연산 증폭기로 K157UD2를 사용합니다. 이 증폭기에는 다음 매개변수가 있습니다. 이득(1kHz의 주파수에서) K = 1800(65dB) , 입력 임피던스 R BX.OU = 500kOhm, 출력 저항 R OUT.OU = 300Ω, 바이어스 전압 U CM = 10mV, 입력 전류 I IN ≤ 500nA. 입력 신호의 레벨은 U IN = 40mV입니다.

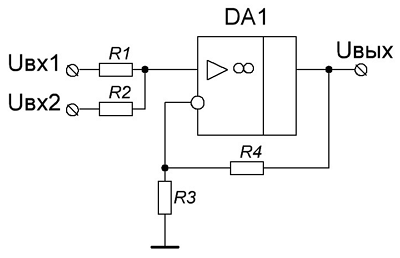

비 반전 가산기

비반전 증폭기의 주제를 계속해서 입력 신호를 추가하는 기능을 수행하고 선형 신호 믹서(믹서)로서의 응용을 찾는 비반전 가산기에 대해 이야기하겠습니다. 예를 들어 여러 소스의 신호를 결합해야 할 때 전력 증폭기의 입력에 공급됩니다. 비반전 가산기의 회로는 아래와 같습니다.

이 회로는 2입력 비반전 증폭기이며 연산 증폭기 DA1, 전류 제한 입력 저항 R1 및 R2, 바이어스 저항 R3 및 피드백 저항 R4로 구성됩니다.

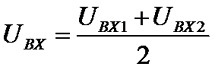

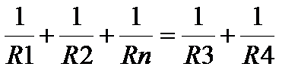

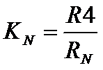

이 회로의 경우 기본 관계는 회로의 입력 전압이 입력 단자의 평균 전압에 해당한다는 사실을 고려하여 간단한 비 반전 증폭기의 회로에 해당합니다

그리고 저항의 저항은 다음 조건을 충족해야 합니다.

다른 채널에 대한 이득은 다음 식에 의해 결정됩니다.

RN은 입력 저항의 저항이며,

KN은 해당 증폭 채널의 이득입니다.

비 반전 가산기 회로의 주요 단점은 제로 전위점이 없기 때문에 다양한 입력의 이득이 독립적이지 않다는 것입니다. 이 단점은 입력 전압 소스의 내부 저항 또는 그 중 하나만 대략적으로 알려져 있거나 작동 중에 변경되는 경우에 나타납니다.

이론은 좋지만 실천이 없는 이론은 허공을 흔드는 것뿐입니다.

만 마일의 여정은 첫 걸음부터 시작됩니다.

(중국 속담)

저녁에 할 일이 없었고 ... 그래서 갑자기 나는 무언가를 납땜하고 싶었습니다. 일종의 ... 전자! .. 솔더 - 솔더. 컴퓨터를 사용할 수 있고 인터넷이 연결되어 있습니다. 우리는 계획을 선택합니다. 그리고 갑자기 잉태 된 주제에 대한 계획은 마차와 작은 카트라는 것이 밝혀졌습니다. 그리고 모든 사람은 다릅니다. 경험이 없고 지식이 거의 없습니다. 어느 것을 선택할 것인가? 그들 중 일부는 일종의 직사각형, 삼각형을 포함합니다. 증폭기, 심지어 작동하는 것까지 ... 작동 방식이 명확하지 않습니다. Stra-a-ashno!.. 불타버리면? 우리는 친숙한 트랜지스터에서 더 간단한 것을 선택합니다! 선택, 납땜, 켜짐 ... HELP !!! 작동하지 않습니다!!! 왜요?

예, "단순함이 도둑질보다 나쁩니다"이기 때문입니다! 그것은 컴퓨터와 같습니다. 가장 빠르고 가장 정교한 게임입니다! 그리고 사무의 경우 가장 단순한 것으로 충분합니다. 트랜지스터도 마찬가지입니다. 회로를 납땜하는 것만으로는 충분하지 않습니다. 아직 설정 방법을 알아야 합니다. "함정"과 "갈퀴"가 너무 많습니다. 그리고 이것은 종종 입문 수준이 아닌 경험을 필요로 합니다. 그럼 흥미진진한 활동을 그만둘까요? 결코 아니다! 이 "삼각형 - 직사각형"을 두려워하지 마십시오. 많은 경우 개별 트랜지스터보다 작업하는 것이 훨씬 쉽습니다. 알고 있다면 - 어떻게!

여기에서 우리는 연산 증폭기(op-amp, 영어로 OpAmp)가 어떻게 작동하는지 이해하고 이제 다룰 것입니다. 동시에 옴의 할아버지의 법칙을 제외하고는 공식을 사용하지 않고 사실상 "손가락에 대한" 그의 작업을 고려할 것입니다. "회로 섹션을 통한 전류( 나)는 양단의 전압에 정비례합니다( 유) 저항에 반비례합니다 ( 아르 자형)»:

I=U/R. (1)

우선 원칙적으로 연산 증폭기가 내부에 정확히 어떻게 배열되어 있는지는 그다지 중요하지 않습니다. 거기에 약간의 스터핑이 있는 "블랙 박스"라고 가정해 보겠습니다. 이 단계에서는 "바이어스 전압", "시프트 전압", "온도 드리프트", "잡음 특성", "공통 모드 억제 계수", "공급 전압 리플 억제 계수"와 같은 연산 증폭기의 매개변수를 고려하지 않습니다. ", "대역폭" 등 이 모든 매개 변수는 연구의 다음 단계에서 중요합니다. 작업의 기본 원칙이 머리에 "정착"될 때 "종이에서는 부드러웠지만 계곡을 잊어 버렸습니다." ...

지금은 연산 증폭기의 매개변수가 이상적이라고 가정하고 일부 신호가 입력에 적용되는 경우 출력에 어떤 신호가 있을 것인지만 고려합니다.

따라서 연산 증폭기(op-amp)는 차동 증폭기입니다. 직류 2개의 입력(반전 및 비반전)과 1개의 출력이 있습니다. 그 외에도 연산 증폭기에는 양극 및 음극의 전원 리드가 있습니다. 이 다섯 가지 결론은 다음에서 찾을 수 있습니다. 거의모든 OS를 지원하며 운영에 기본적으로 필요합니다.

연산 증폭기는 최소 50,000 ... 100,000의 엄청난 이득을 갖지만 실제로는 훨씬 더 많습니다. 따라서 첫 번째 근사값으로 무한대와 같다고 가정할 수도 있습니다.

"차동"("차이"는 영어에서 "차이", "차이", "차이"로 번역됨)이라는 용어는 연산 증폭기의 출력 전위가 입력 간의 전위차에 의해서만 영향을 받는다는 것을 의미하며, ~에 관계없이그들로부터 순수한의미와 극성.

"DC"라는 용어는 연산 증폭기가 0Hz에서 시작하는 입력 신호를 증폭한다는 것을 의미합니다. 상위 주파수 범위( 주파수 범위) 연산 증폭기에 의해 증폭되는 신호의 )는 구성되는 트랜지스터의 주파수 특성, 연산 증폭기를 사용하여 구축된 회로의 이득 등과 같은 많은 요인에 따라 달라집니다. 그러나이 문제는 이미 그의 작업에 대한 초기 지인의 범위를 벗어나 여기에서 고려되지 않습니다.

연산 증폭기 입력은 수십/수백 MegaOhm 또는 GigaOhm과 같은 매우 높은 입력 임피던스를 갖습니다(그리고 기억에 남는 K140UD1에서만, 그리고 K140UD5에서도 30...50 kOhm에 불과했습니다). 입력의 이러한 높은 임피던스는 입력 신호에 거의 영향을 미치지 않는다는 것을 의미합니다.

따라서 이론적 이상에 높은 수준으로 근사하면 다음과 같이 가정할 수 있습니다. 현재의 연산 증폭기의 입력으로 흐르지 않습니다. . 그것 - 첫 번째분석에 적용되는 중요한 규칙 OS 작업. 그것이 무엇인지 잘 기억하십시오. 뿐 OU 자체, 하지만 계획 그것의 사용으로!

"반전" 및 "비반전"이라는 용어는 무엇을 의미합니까? 반전이 결정되는 것과 일반적으로 어떤 종류의 "동물"과 관련하여 이것은 신호 반전입니까?

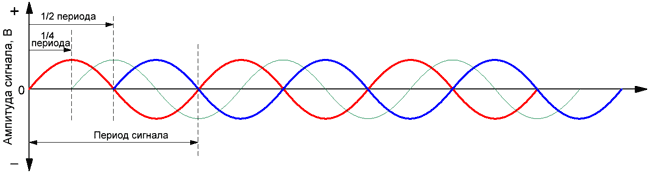

라틴어에서 번역 된 "inversio"라는 단어의 의미 중 하나는 "포장", "쿠데타"입니다. 다시 말해, 반전은 미러 이미지( 미러링) 수평축 X에 대한 신호(시간 축). 그림에. 1은 많은 것 중 몇 가지를 보여줍니다. 옵션신호 반전, 여기서 직접(입력) 신호는 빨간색으로 표시되고 반전(출력) 신호는 파란색으로 표시됩니다.

쌀. 1 신호 반전의 개념

제로 라인(그림 1, A, B에서와 같이) 신호 반전에 특히 주목해야 합니다. 묶이지 않은! 신호는 역 및 비대칭일 수 있습니다. 예를 들어, 둘 다 양수 값의 영역에만 있고(그림 1, B), 이는 디지털 신호 또는 단극 전원 공급 장치에서 일반적으로 사용됩니다(이는 나중에 논의됨), 또는 둘 다 부분적으로 양수 및 부분적으로 음의 영역에서(그림 1, B, D). 다른 옵션도 가능합니다. 주요 조건은 상호 반사임의로 선택된 일부 수준(예: 인위적인 중간점, 나중에 논의됨)에 대한 상대적입니다. 다시 말해, 극성신호도 결정 요인이 아닙니다.

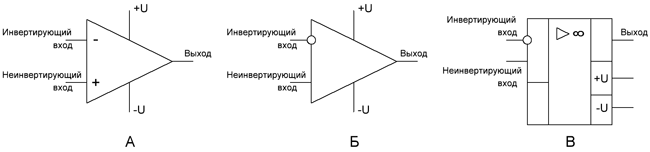

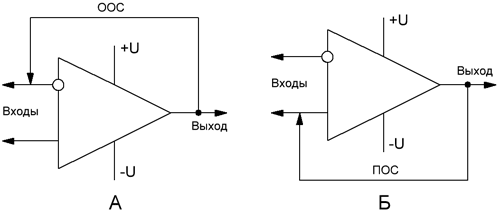

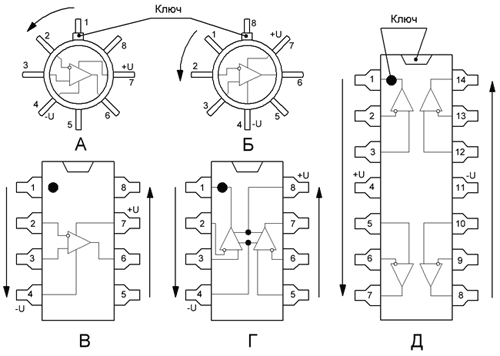

다양한 방식으로 회로도에서 OU를 묘사하십시오. 해외에서는 OS가 이전에 묘사되었으며 지금도 종종 이등변 삼각형의 형태로 묘사됩니다(그림 2, A). 반전 입력은 빼기 기호로 표시되고, 비 반전 입력은 삼각형 내부에 더하기 기호로 표시됩니다. 이 기호는 각 입력의 전위가 다른 것보다 더 긍정적이거나 더 부정적이어야 한다는 것을 전혀 의미하지 않습니다. 그것들은 단순히 출력 전위가 입력에 적용된 전위에 어떻게 반응하는지를 나타냅니다. 결과적으로 특히 초보자에게 예기치 않은 "갈퀴"가 될 수 있는 전원 리드와 혼동하기 쉽습니다.

쌀. 2 조건부 그래픽 이미지의 변형(UGO)

연산 증폭기

GOST 2.759-82(ST SEV 3336-81)가 시행되기 전의 국내 조건부 그래픽 이미지(UGO) 시스템에서 OU도 삼각형으로 표시되었으며 반전 입력만 반전 기호가 있는 원 출력과 삼각형의 교차점(그림 2, B), 이제 - 직사각형 형태(그림 2, C).

그림에서 연산증폭기를 지정할 때 편의상 반전 입력과 비반전 입력을 서로 바꾸어 사용할 수 있지만, 전통적으로는 상단에 반전 입력을, 하단에 비반전 입력을 표시했습니다. 전원 핀은 일반적으로 항상 한 방향으로 배치됩니다(위쪽은 양극, 아래쪽은 음극).

연산 증폭기는 거의 항상 네거티브 피드백(NFB) 회로에 사용됩니다.

피드백은 증폭기의 출력 전압의 일부를 입력에 적용하는 효과로, 입력 전압에 대수적으로(부호에 따라 다름) 더해진다. 신호 합산의 원리는 아래에서 논의될 것이다. 반전 또는 비반전 연산 증폭기의 입력에 따라 OS가 공급되고 출력 신호의 일부가 반전 입력(그림 3, A)에 적용될 때 음의 피드백(NFB)이 발생합니다. 포지티브 피드백(PIC), 출력 신호의 일부가 각각 비반전 입력으로 공급될 때(그림 3, B).

쌀. 3 피드백 형성의 원리(OS)

첫 번째 경우 출력은 입력의 역수이므로 입력에서 뺍니다. 그 결과, 스테이지의 전체 게인이 감소합니다. 두 번째 경우에는 입력에 추가되고 캐스케이드의 전체 게인이 증가합니다.

언뜻보기에 POS가 긍정적 인 영향을 미치는 것처럼 보일 수 있으며 OOS는 완전히 쓸모없는 사업입니다. 이득을 줄이는 이유는 무엇입니까? 이것이 바로 미국 특허 심사관들이 1928년에 Harold S. Black이 생각했던 것과 같습니다. 시험을 마친 OS 특허. 그러나 증폭을 희생하면서 선형성, 주파수 범위 등과 같은 회로의 다른 중요한 매개변수를 크게 개선했습니다. OOS가 깊을수록 전체 회로의 특성이 연산 증폭기의 특성에 의존하는 특성이 줄어듭니다.

그러나 PIC(Op-Amp 자체의 큰 이득을 감안할 때)는 회로의 특성에 반대의 영향을 미치며 가장 불쾌한 것은 자체 여기를 유발한다는 것입니다. 물론, 예를 들어 발전기, 히스테리시스가 있는 비교기(나중에 자세히 설명) 등에서 의식적으로 사용되지만 일반보기연산 증폭기가 있는 증폭기 회로의 작동에 미치는 영향은 다소 부정적이며 응용 프로그램에 대한 매우 철저하고 합리적인 분석이 필요합니다.

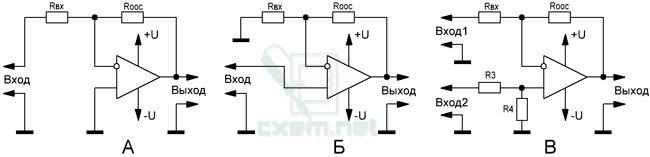

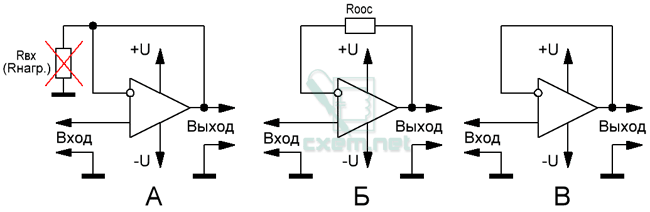

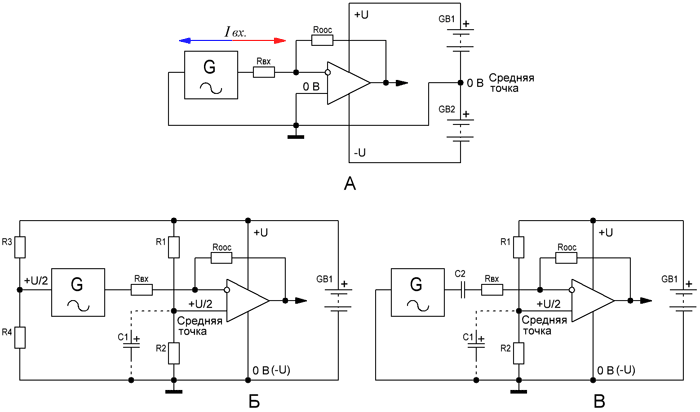

OS에는 두 가지 입력이 있으므로 OS를 사용하여 다음과 같은 주요 유형을 포함할 수 있습니다(그림 4).

쌀. 4 OS를 켜기 위한 기본 구성표

ㅏ) 반전 (그림 4, A) - 신호가 반전 입력에 적용되고 비 반전 입력이 기준 전위에 직접 연결됩니다(사용되지 않음).

비) 비 반전 (그림 4, B) - 신호가 비 반전 입력에 적용되고 반전 입력이 기준 전위에 직접 연결됩니다(사용되지 않음).

안에) 미분 (그림 4, B) - 신호는 반전 및 비반전의 두 입력 모두에 공급됩니다.

이러한 계획의 운영을 분석하려면 다음을 고려해야 합니다. 초가장 중요한 규칙, OS 작동이 적용되는: 연산 증폭기의 출력은 입력 간의 전압 차이가 0인 경향이 있습니다..

그러나 모든 문구는 다음과 같아야 합니다. 필요하고 충분하다그것을 따르는 경우의 전체 하위 집합을 제한합니다. 위의 공식은 모든 "고전주의"에 대해 출력이 "영향을 미치려는" 입력에 대한 정보를 제공하지 않습니다. 이를 기반으로 연산 증폭기는 입력에서 전압을 균등화하여 "내부에서" 어딘가에서 전압을 적용하는 것으로 나타났습니다.

그림의 다이어그램을 자세히 살펴보면 4, 모든 경우에 OOC(Rooc을 통해)가 출구에서 시작되었음을 알 수 있습니다. 뿐이 규칙을 다음과 같이 다시 작성해야 하는 이유를 제공하는 반전 입력: 전압 켜기 OOS로 덮인 연산 증폭기의 출력은 반전 입력의 전위가 비반전 입력의 전위와 같도록 하는 경향이 있습니다..

이 정의에 따라 OOS와 함께 OA를 포함할 때 "선도"는 비반전 입력이고 "슬레이브"는 반전 입력입니다.

연산 증폭기의 작동을 설명할 때 반전 입력의 전위는 종종 "가상 0" 또는 "가상 중간점"이라고 합니다. 라틴어 "virtus"의 번역은 "상상의", "상상의"를 의미합니다. 가상 물체는 물질적 현실의 유사한 물체의 거동에 가깝게 행동합니다. 즉, 입력 신호(FOS의 작용으로 인해)의 경우 반전 입력은 비반전 입력과 동일한 전위에 직접 연결된 것으로 간주될 수 있습니다. 그러나 "가상 제로"는 연산 증폭기의 바이폴라 전원 공급 장치에서만 발생하는 특별한 경우입니다. 유니폴라 전원 공급 장치(아래에서 설명)를 사용할 때와 다른 많은 스위칭 회로에서는 비반전 또는 반전 입력에 0이 없습니다. 따라서 OS 작동 원리에 대한 초기 이해를 방해하기 때문에 이 용어를 사용하지 않을 것에 동의합니다.

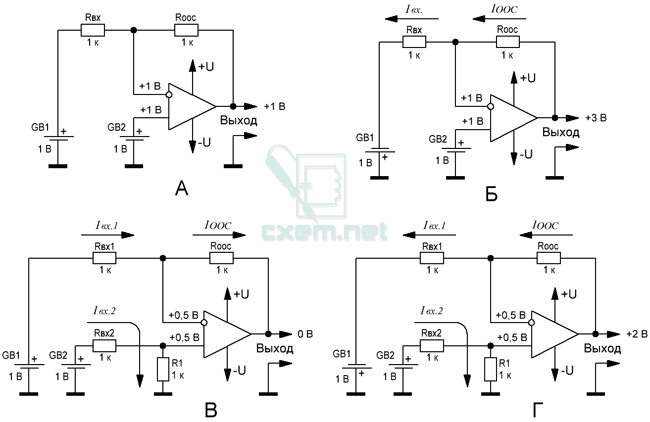

이러한 관점에서 우리는 Fig. 4. 동시에 분석을 단순화하기 위해 공급 전압이 여전히 양극성이며 값(예: ±15V)이 서로 동일하고 중간점(공통 버스 또는 "접지")이 상대적인 것으로 가정합니다. 입력 및 출력 전압을 계산합니다. 또한 분석은 직류에서 수행되기 때문에. 시간의 각 순간에 변화하는 교류 신호는 직류 값의 샘플로 나타낼 수도 있습니다. 모든 경우에 Rooc을 통한 피드백은 연산 증폭기의 출력에서 반전 입력으로 연결됩니다. 차이점은 입력 전압이 적용되는 입력에만 있습니다.

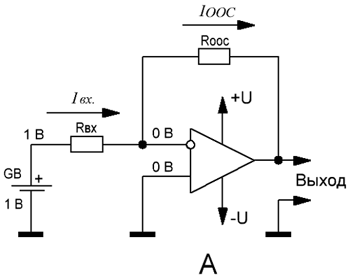

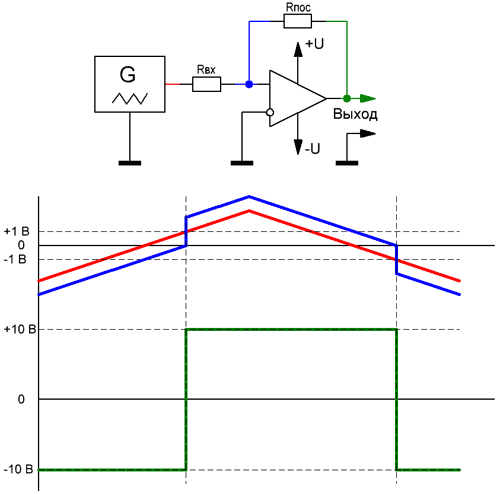

하지만) 반전켜기(그림 5).

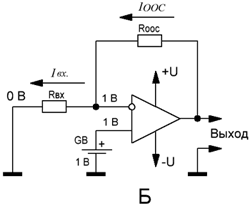

쌀. 5 반전 연결에서 연산 증폭기의 작동 원리

비 반전 입력의 전위는 0입니다. 왜냐하면 중간 지점("그라운드")에 연결됩니다. 중간점(GB에서)에 대해 +1V와 동일한 입력 신호가 입력 저항 Rin의 왼쪽 단자에 적용됩니다. 저항 Rooc과 Rin이 서로 동일하고 1kOhm(그들의 총 저항은 2kOhm)이라고 가정합시다.

규칙 2에 따르면 반전 입력은 비반전 입력과 동일한 전위, 즉 0V를 가져야 합니다. 따라서 Rin에 +1V의 전압이 인가됩니다. 옴의 법칙에 따라 전류가 흐릅니다. 나입력= 1V / 1000옴 = 0.001A(1mA). 이 전류의 흐름 방향은 화살표로 표시됩니다.

Rooc과 Rin은 분배기로 연결되어 있고 규칙 1에 따라 연산 증폭기 입력은 전류를 소비하지 않으므로 이 분배기의 중간 지점에서 전압이 0V가 되기 위해서는 오른쪽에 전압을 인가해야 합니다. Rooc의 출력 마이너스 1V, 그리고 그것을 통해 흐르는 전류 나이런또한 1mA와 같아야 합니다. 즉, 왼쪽 단자 Rin과 오른쪽 단자 Rooc 사이에 2V의 전압이 인가되고, 이 분배기에 흐르는 전류는 1mA(2V/(1kΩ + 1kΩ) = 1mA), 즉 나 입력 = 나 이런 .

입력에 음의 극성 전압이 인가되면 연산 증폭기의 출력은 양의 극성 전압이 됩니다. 모든 것이 동일하며 Rooc과 Rin을 통한 전류의 흐름을 나타내는 화살표만 반대 방향으로 향하게 됩니다.

따라서 Rooc과 Rin의 값이 같으면 연산 증폭기의 출력 전압은 입력 전압과 크기는 같지만 극성은 반대입니다. 그리고 우리는 얻었다 반전 연발총 . 이 방식은 기본적으로 인버터인 회로를 사용하여 수신된 신호를 반전해야 하는 경우에 자주 사용됩니다. 예를 들어, 대수 증폭기.

이제 Rin을 1kOhm으로 동일하게 유지하고 동일한 +1V 입력 신호로 Rooc 저항을 2kOhm으로 증가시키겠습니다.총 분배기 저항 Rooc+Rin은 3kOhm으로 증가했습니다. 0V의 전위(비반전 입력의 전위와 동일)가 중간점에 유지되려면 Rin을 통해와 동일한 전류(1mA)가 Rooc을 통해 흘러야 합니다. 따라서 Rooc(연산 증폭기의 출력 전압) 양단의 전압 강하는 이미 2V여야 합니다. 연산 증폭기의 출력에서 전압은 -2V입니다.

Rooc의 값을 10kOhm으로 높이자. 이제 동일한 다른 조건에서 연산 증폭기의 출력 전압은 이미 10V가 됩니다. 와우! 마침내 우리는 얻었다 반전 증폭기

! 그의 출력 전압저항 Rooc의 배만큼 입력(즉, 이득 Ku)이 저항 Rin보다 큽니다. 내가 수식을 사용하지 않겠다고 맹세했더라도 이것을 방정식으로 표시해 보겠습니다.

Ku \u003d - Uout / Uin \u003d - Rooc / Rin. (2)

방정식 오른쪽 분수 앞의 빼기 기호는 출력 신호가 입력에 대해 역이라는 것을 의미합니다. 그리고 더 이상 아무것도!

이제 저항 Rooc을 20kOhm으로 높이고 어떤 일이 발생하는지 분석해 보겠습니다. 공식 (2)에 따르면 Ku \u003d 20 및 1V의 입력 신호로 출력은 20V의 전압이어야 합니다. 그러나 거기에 없었습니다! 우리는 이전에 연산 증폭기의 공급 전압이 ± 15V에 불과하다고 가정했습니다. 그러나 15V도 얻을 수 없습니다(어떤 이유로 약간 낮음). "머리 위로 점프할 수 없다(공급 전압)"! 이러한 회로 정격 남용의 결과로 연산 증폭기의 출력 전압은 공급 전압에 "안착"됩니다( 연산 증폭기의 출력이 포화 상태가 됨). 분배기 RoocRin( 나입력 = 나이런)을 위반하면 반전 입력에 전위가 나타나며 이는 비반전 입력의 전위와 다릅니다. 규칙 2는 더 이상 적용되지 않습니다.

입력 저항 반전 증폭기입력 신호 소스(GB)의 모든 전류가 이를 통해 흐르기 때문에 저항 Rin과 같습니다.

이제 Rooc 상수를 공칭 값이 10kOhm인 변수로 교체해 보겠습니다(그림 6).

쌀. 6 가변 이득 반전 증폭기 회로

슬라이더의 오른쪽(회로에 따라) 위치에서 이득은 Rooc / Rin = 10kOhm / 1kOhm = 10이 됩니다. Rooc 슬라이더를 왼쪽으로 움직이면(저항 감소) 회로의 이득은 감소하고 마지막으로 맨 왼쪽 위치에서 위 공식의 분자가 0이 되기 때문에 0이 됩니다. 어느 분모의 값. 출력은 또한 입력 신호의 모든 값과 극성에 대해 0이 됩니다. 이러한 방식은 예를 들어 게인을 0에서 조정해야 하는 믹서와 같은 오디오 증폭 회로에서 자주 사용됩니다.

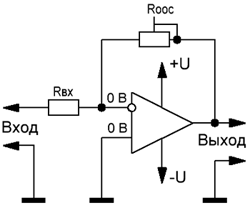

비) 비 반전켜기(그림 7).

쌀. 7 비 반전 포함에서 연산 증폭기의 작동 원리

Rin의 왼쪽 핀은 중간점("접지")에 연결되고 +1V와 동일한 입력 신호는 비반전 입력에 직접 적용됩니다. 위에서 분석의 뉘앙스가 "씹혀"있기 때문에 여기서는 중요한 차이점에만주의를 기울일 것입니다.

분석의 첫 번째 단계에서 우리는 저항 Rooc과 Rin을 서로 동일하고 1kOhm과 동일하게 취합니다. 왜냐하면 비 반전 입력에서 전위는 +1V이고 규칙 2에 따라 반전 입력에 동일한 전위(+1V)가 있어야 합니다(그림 참조). 이렇게 하려면 Rooc 저항(연산 증폭기의 출력)의 오른쪽 단자에 +2V의 전압이 있어야 합니다. 나입력그리고 나이런, 1mA와 같으므로 이제 반대 방향(화살표로 표시)으로 저항 Rooc 및 Rin을 통해 흐릅니다. 우리는 그것을 얻었다 비 반전 증폭기 +1V의 입력이 +2V의 출력을 생성하기 때문에 이득이 2입니다.

이상하지 않나요? 정격은 반전 연결에서와 동일하며(유일한 차이점은 신호가 다른 입력에 적용된다는 것입니다) 이득이 분명합니다. 이에 대해서는 잠시 후에 살펴보겠습니다.

이제 Rooc 값을 2kOhm으로 높입니다. 전류의 균형을 유지하기 위해 나입력 = 나이런반전 입력의 전위는 +1V이고 연산 증폭기의 출력은 이미 +3V여야 합니다. Ku \u003d 3V / 1V \u003d 3!

Ku의 값을 비 반전 연결과 반전 연결과 비교하면 Rooc 및 Rin 등급이 동일하며 모든 경우에 이득이 1만큼 더 큽니다. 공식을 도출합니다.

Ku \u003d Uout / Uin + 1 \u003d (Rooc / Rin) + 1 (3)

왜 이런 일이 발생합니까? 예, 매우 쉽습니다! NFB는 반전 연결에서와 정확히 동일하게 작동하지만 규칙 2에 따르면 비반전 입력의 전위는 항상 비반전 연결에서 반전 입력의 전위에 추가됩니다.

따라서 비 반전 포함으로 1과 같은 이득을 얻는 것이 불가능합니까? 왜 안 돼, 왜 안 돼? Fig. 4에서 분석한 것처럼 Rooc의 값을 줄여보자. 6. 값이 0일 때 - 규칙 2에 따라 반전 입력(그림 8, A)으로 출력을 단락시킴으로써 출력은 반전 입력의 전위가 전위와 동일한 전압을 갖게 됩니다. 비 반전 입력, 즉 +1 V. 우리는 다음을 얻습니다. Ku \u003d 1 V / 1 V \u003d 1 (!) 음, 반전 입력은 전류를 소비하지 않고 그것과 출력 사이에 전위차가 없기 때문에 이 회로에는 전류가 흐르지 않습니다.

쌀. 8 전압 팔로워로 연산 증폭기를 켜는 방식

Rin은 일반적으로 불필요합니다. 그것은 연산 증폭기의 출력이 작동해야 하는 부하와 병렬로 연결되며 출력 전류는 이를 통해 헛되이 흐를 것입니다. 그리고 Rooc을 떠나 Rin을 제거하면 어떻게 될까요?(그림 8, B)? 그런 다음 이득 공식 Ku = Roos / Rin + 1에서 저항 Rin은 이론적으로 무한대에 가까워집니다. , 여전히 0은 여전히 동일하지 않음), Rooc/Rin 비율은 0과 동일합니다. 공식에는 하나만 남아 있습니다. Ku \u003d + 1. 이 회로의 이득이 1보다 작을 수 있습니까? 아니요, less는 어떤 상황에서도 작동하지 않습니다. 비뚤어진 염소의 게인 공식에서 "추가"단위를 돌아 다닐 수 없습니다 ...

모든 "추가"저항을 제거한 후 회로를 얻습니다. 비 반전 연발총 그림에 나와 있습니다. 8, V.

언뜻보기에 그러한 계획은 실용적인 의미가 없습니다. 왜 우리는 단일, 심지어는 역이 아닌 "증폭"이 필요한가요? 신호를 더 보낼 수는 없습니다 ??? 그러나 이러한 구성표는 매우 자주 사용되며 여기에 이유가 있습니다. 규칙 1에 따르면 전류는 연산 증폭기의 입력으로 흐르지 않습니다. 입력 임피던스 비 반전 팔로워는 매우 큽니다. 동일한 수십, 수백, 심지어 수천 MΩ입니다(그림 7에 따른 회로에도 동일하게 적용됨)! 그러나 출력 저항은 매우 작습니다(Ohm의 분수!). 규칙 2에 따라 비반전 입력에서와 반전 입력에서 동일한 전위를 유지하려고 시도하는 연산 증폭기의 출력은 "온 힘을 다해 휘젓는다". 유일한 제한 사항은 연산 증폭기의 허용 가능한 출력 전류입니다.

그러나 여기에서 우리는 약간 옆으로 흔들리고 연산 증폭기의 출력 전류 문제를 조금 더 자세히 고려할 것입니다.

대부분의 범용 연산 증폭기의 경우 기술 사양에 따르면 출력에 연결된 부하의 저항은 다음과 같아야 합니다. 더 적은 2k옴 더 - 원하는 만큼. 훨씬 적은 수의 경우 1kOhm(K140UD ...)입니다. 이는 최악의 조건에서 최대 공급 전압(예: ±16V 또는 총 32V), 출력과 전원 레일 중 하나 사이에 연결된 부하, 반대 극성의 최대 출력 전압, 약 30V의 전압이 부하에 적용됩니다.이 경우 전류는 30V / 2000Ohm = 0.015A(15mA)입니다. 너무 적지도 적지도 않습니다. 다행히 대부분의 범용 연산 증폭기에는 과전류 보호 기능이 내장되어 있습니다. 일반적인 최대 출력 전류는 25mA입니다. 보호 기능은 연산 증폭기의 과열 및 고장을 방지합니다.

공급 전압이 최대 허용치가 아니면 최소 부하 저항을 비례적으로 줄일 수 있습니다. 7.5 ... 8 V(총 15 ... 16 V)의 전원 공급 장치를 사용하면 1kOhm이 될 수 있습니다.

에) 미분켜기(그림 9).

쌀. 9 차동 연결에서 연산 증폭기의 작동 원리

따라서 동일한 정격 Rin 및 Rooc이 1kOhm이고 +1V와 동일한 전압이 회로의 두 입력에 모두 적용된다고 가정해 보겠습니다(그림 9, A). 저항 Rin의 양쪽 전위는 서로 같기 때문에(저항 양단의 전압은 0) 전류가 흐르지 않습니다. 이것은 저항 Rooc를 통과하는 전류도 0임을 의미합니다. 즉, 이 두 저항은 아무 기능도 하지 않습니다. 사실, 우리는 실제로 비반전 추종자를 얻었습니다(그림 8과 비교). 따라서 출력에서 비 반전 입력, 즉 +1V와 동일한 전압을 얻게 됩니다. 회로의 반전 입력(GB1을 뒤집음)에서 입력 신호의 극성을 변경하고 마이너스 1V를 적용해 보겠습니다. (그림 9, B). 이제 Rin 단자 사이에 2V의 전압이 적용되고 전류가 흐릅니다. 나안에\u003d 2 mA (이것이 왜 그런지 자세히 설명할 필요가 없기를 바랍니다.) 이 전류를 보상하기 위해서는 Rooc에도 2mA의 전류가 흘러야 합니다. 그리고 이를 위해 연산 증폭기의 출력은 +3V의 전압을 가져야 합니다.

그것이 비 반전 증폭기의 이득 공식에 추가의 악의적 인 "미소"가 나타난 곳입니다. 그러한 것으로 밝혀졌습니다. 쉽게 한차동 스위칭에서 이득의 차이는 비반전 입력의 전위만큼 출력 신호를 지속적으로 이동시킵니다. 문제! 단, "먹혀도 출구는 2개 이상 남아있다." 이것은 우리가 이 추가 내포물을 "중화"하기 위해 반전 및 비반전 내포물의 이득을 어떻게든 균등화할 필요가 있음을 의미합니다.

이렇게하려면 입력 신호를 비 반전 입력에 직접 적용하지 않고 분배기 Rin2, R1을 통해 적용합시다 (그림 9, B). 그들의 교단도 1kOhm에 대해 살펴보겠습니다. 이제 연산 증폭기의 비반전(따라서 반전에서도) 입력에서 +0.5V의 전위가 있고 전류가 이를 통해 흐릅니다(및 Rooc). 나안에 = 나이런\u003d 0.5mA, 연산 증폭기의 출력이 0V와 동일한 전압을 가져야 함을 보장합니다. 휴! 우리는 우리가 원하는 것을 얻었다! 회로의 두 입력에서 동일한 크기 및 극성 신호(이 경우 +1V, 그러나 마이너스 1V 및 기타 디지털 값에 대해 동일함)에서 연산 출력에서 0 전압이 유지됩니다. amp, 입력 신호의 차이와 동일합니다.

반전 입력에 음극성 마이너스 1V의 신호를 적용하여 이 추론을 확인합시다(그림 9, D). 어디에서 나안에 = 나이런= 2mA, 출력은 +2V여야 합니다. 모든 것이 확인되었습니다! 출력 레벨은 입력 간의 차이에 해당합니다.

물론 Rin1과 Rooc이 같으면(각각 Rin2와 R1) 증폭되지 않습니다. 이렇게 하려면 이전에 포함된 연산 증폭기(반복하지 않겠습니다)를 분석할 때 수행한 대로 Rooc 및 R1의 값을 늘려야 합니다. 엄격하게 비율을 존중하십시오:

Rooc / Rin1 = R1 / Rin2. (4)

실제로 그러한 포함을 통해 우리가 얻는 것이 무엇입니까? 그리고 우리는 놀라운 특성을 얻습니다. 출력 전압은 크기와 극성이 서로 동일한 경우 입력 신호의 절대 값에 의존하지 않습니다. 차분(미분) 신호만 출력됩니다. 이를 통해 두 입력에서 동일하게 작용하는 잡음의 배경에 대해 매우 작은 신호를 증폭할 수 있습니다. 예를 들어, 50Hz 산업용 주파수 주전원 픽업의 배경에 대한 동적 마이크의 신호입니다.

그러나이 꿀 배럴에는 불행히도 연고에 파리가 있습니다. 첫째, 평등(4)은 매우 엄격하게 준수되어야 합니다(최대 1/10, 때로는 1/100%!). 그렇지 않으면 회로에 작용하는 전류의 불균형이 발생하므로 차("역위상") 신호 외에 결합된("공통 모드") 신호도 증폭됩니다.

이 용어의 본질을 이해합시다(그림 10).

쌀. 10 신호 위상 편이

신호의 위상은 시간의 원점에 대한 신호 주기의 원점 오프셋을 특성화하는 값입니다. 시간의 근원과 주기의 근원은 모두 임의로 선택되기 때문에 하나의 위상은 정기 간행물신호는 물리적 의미가 없습니다. 그러나 양자의 위상차는 정기 간행물신호는 물리적 의미를 갖는 양이며 다른 신호에 비해 신호 중 하나의 지연을 반영합니다. 기간의 시작으로 간주되는 것은 중요하지 않습니다. 기간의 시작 지점에 대해 양의 기울기로 0 값을 취할 수 있습니다. 가능합니다 - 최대. 모든 것이 우리의 힘입니다.

그림에. 9에서 빨간색은 원래 신호를 나타내고 녹색은 원래 신호에 대해 1/4 주기로 이동하고 파란색은 ½ 주기를 나타냅니다. 빨간색과 파란색 곡선을 그림의 곡선과 비교하면 2, B, 서로 상호작용을 하고 있음을 알 수 있다. 역. 따라서 "동위상 신호"는 각 지점에서 서로 일치하는 신호이고 "반위상 신호"는 역서로 상대적.

동시에 컨셉은 반전개념보다 넓은 단계, 왜냐하면 후자는 규칙적으로 반복되는 주기적인 신호에만 적용됩니다. 그리고 개념 반전오디오 신호, 디지털 시퀀스 또는 정전압과 같은 비주기적인 신호를 포함한 모든 신호에 적용 가능합니다. 에게 단계가 일관된 값이면 신호는 적어도 특정 간격에 걸쳐 주기적이어야 합니다. 그렇지 않으면 위상과 기간이 모두 수학적 추상화로 바뀝니다.

둘째, 동일한 정격 Rooc = R1 및 Rin1 = Rin2인 차동 연결의 반전 및 비반전 입력은 입력 저항이 다릅니다. 반전 입력의 입력 저항이 Rin1 값에 의해서만 결정되면 비반전 입력은 값에 의해 결정됩니다. 연속적으로포함된 Rin2 및 R1(연산 증폭기 입력이 전류를 소비하지 않는다는 것을 잊지 않았습니까?). 위의 예에서는 각각 1kΩ과 2kΩ이 됩니다. 그리고 본격적인 증폭 단계를 얻기 위해 Rooc과 R1을 높이면 차이가 훨씬 더 크게 증가합니다. Ku \u003d 10 - 각각 최대 1kOhm과 11kOhm!

불행히도 실제로는 Rin1 = Rin2 및 Rooc = R1 등급이 일반적으로 설정됩니다. 그러나 이는 두 입력의 신호 소스가 매우 낮은 경우에만 허용됩니다. 출력 임피던스. 그렇지 않으면이 증폭 단계의 입력 임피던스로 분배기를 형성하고 이러한 "분배기"의 분배 계수가 다르기 때문에 결과는 분명합니다. 이러한 저항 값을 가진 차동 증폭기는 억제 기능을 수행하지 않습니다 공통 모드(결합) 신호를 보내거나 이 기능을 제대로 수행하지 못합니다.

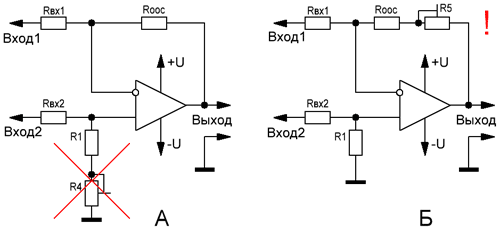

이 문제를 해결하는 방법 중 하나는 연산 증폭기의 반전 및 비반전 입력에 연결된 저항 값의 불평등일 수 있습니다. 즉, Rin2 + R1 = Rin1입니다. 또 다른 중요한 점은 평등의 정확한 준수를 달성하는 것입니다(4). 일반적으로 이것은 R1을 두 개의 저항으로 분할하여 달성됩니다. 하나는 상수(보통 원하는 값의 90%)이고, 다른 하나는 저항이 필요한 값의 20%인 변수(R2)입니다(그림 11, A).

쌀. 11 차동 증폭기 밸런싱 옵션

경로는 일반적으로 허용되지만 다시 이 균형 조정 방법을 사용하면 약간이지만 비반전 입력의 입력 임피던스가 변경됩니다. Rooc은 반전 입력의 입력 저항 형성에 참여하지 않기 때문에 Rooc과 직렬로 튜닝 저항(R5)을 포함하는 훨씬 더 안정적인 옵션(그림 11, B). 가장 중요한 것은 옵션 "A"(Rooc / Rin1 = R1 / Rin2)와 유사한 교단 비율을 유지하는 것입니다.

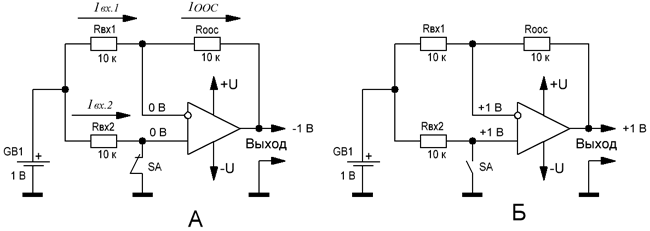

차동 스위칭에 대해 이야기하고 리피터를 언급했기 때문에 흥미로운 회로 하나를 설명하고자 합니다(그림 12).

쌀. 12 전환된 반전/비반전 팔로워 회로

입력 신호는 회로의 두 입력(반전 및 비반전)에 동시에 적용됩니다. 모든 저항기(Rin1, Rin2 및 Rooc)의 정격은 서로 동일합니다(이 경우 실제 값: 10 ... 100kOhm). SA 키가 있는 연산 증폭기의 비반전 입력은 공통 버스로 닫힐 수 있습니다.

키의 닫힌 위치 (그림 12, A)에서 저항 Rin2는 회로 작동에 참여하지 않습니다 (전류 만 "쓸모없이"흐릅니다. 나vx2신호 소스에서 공통 버스로). 우리는 얻는다 반전 추종자마이너스 1과 같은 이득으로 (그림 6 참조). 그러나 SA 키가 열린 위치에 있으면(그림 12, B) 다음을 얻습니다. 비 반전 추종자+1과 같은 이득으로.

이 체계의 작동 원리는 약간 다른 방식으로 표현될 수 있습니다. SA 키가 닫히면 이득이 마이너스 1인 반전 증폭기로 작동하고 열리면 - 동시에(!) 그리고 이득이 마이너스 1인 반전 증폭기와 +2 이득이 있는 비반전 증폭기로서 여기서 Ku = +2 + (-1) = +1입니다.

이 형식에서 이 회로는 예를 들어 설계 단계에서 입력 신호의 극성을 알 수 없는 경우(예: 장치가 설정될 때까지 액세스할 수 없는 센서에서) 사용할 수 있습니다. 그러나 트랜지스터(예: 전계 효과 트랜지스터)를 키로 사용하는 경우 다음을 사용하여 입력 신호에서 제어됩니다. 비교기(아래에서 논의됨), 우리는 동기 검출기(동기 정류기). 물론 이러한 계획의 특정 구현은 OS 작동에 대한 초기 지식을 넘어서므로 여기에서 다시 자세히 고려하지 않을 것입니다.

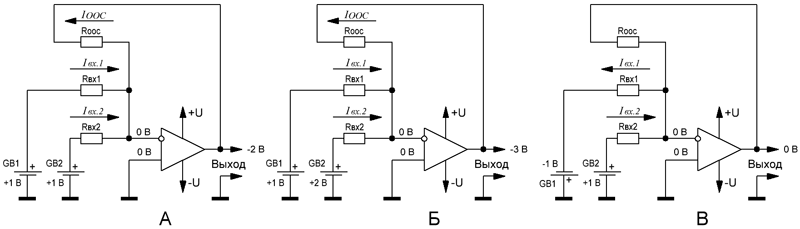

이제 입력 신호를 합산하는 원리 (그림 13, A)를 고려하고 동시에 저항 Rin과 Rooc의 값이 실제로 어떤 값이 되어야 하는지 알아낼 것입니다.

쌀. 13 반전 가산기의 작동 원리

우리는 이미 위에서 논의한 반전 증폭기(그림 5)를 기본으로 삼고 하나가 아닌 두 개의 입력 저항 Rin1과 Rin2를 연산 증폭기의 입력에 연결합니다. 지금까지 "교육적" 목적으로 Rooc을 포함한 모든 저항의 저항은 1kOhm과 같습니다. 왼쪽 단자 Rin1 및 Rin2에 +1V와 동일한 입력 신호를 공급합니다. 1mA와 동일한 전류가 이 저항을 통해 흐릅니다(왼쪽에서 오른쪽으로 화살표로 표시됨). 반전 입력에서 비반전 입력(0V)과 동일한 전위를 유지하려면 입력 전류(1mA + 1mA = 2mA)의 합과 같은 전류가 Rooc 저항을 통해 흐르고 다음과 같이 표시됩니다. 반대 방향(오른쪽에서 왼쪽으로)을 가리키는 화살표는 연산 증폭기의 출력 전압이 마이너스 2V여야 합니다.

반전 증폭기의 입력에 +2V가 적용되거나(그림 5), Rin의 값이 절반인 경우 동일한 결과(출력 전압 - 2V)를 얻을 수 있습니다. 최대 500옴. 저항 Rin2에 인가되는 전압을 최대 +2V까지 증가시키자(그림 13, B). 출력에서 입력 전압의 합과 동일한 마이너스 3V의 전압을 얻습니다.

두 개의 입력이 있을 수는 없지만 원하는 만큼 입력할 수 있습니다. 이 회로의 작동 원리는 다음과 같이 변경되지 않습니다. 어떤 경우에도 출력 전압은 연산의 반전 입력에 연결된 저항을 통과하는 전류의 대수적 합(기호를 고려하여!)에 정비례합니다. -amp(등급에 반비례), 숫자에 관계없이.

그러나 반전 가산기(그림 13, B)의 입력에 +1V 및 -1V와 동일한 신호가 적용되면 이를 통해 흐르는 전류는 다른 방향으로 흐르고 서로 상쇄되고 출력은 0V가 됩니다. 이 경우 저항 Rooc를 통해 전류가 흐르지 않습니다. 즉, Rooc을 통해 흐르는 전류는 다음과 같이 대수적으로 합산됩니다. 입력전류.

여기서 중요한 점은 다음과 같습니다. 우리가 작은 입력 전압(1 ... 3 V)으로 작동하는 동안 널리 사용되는 연산 증폭기의 출력은 Rooc에 이러한 전류(1 ... 3 mA)를 제공할 수 있었습니다. 연산 증폭기의 출력에 연결된 부하에는 다른 것이 남아 있습니다. 그러나 입력 신호의 전압이 최대 허용치(공급 전압에 근접)까지 증가하면 전체 출력 전류가 Rooc으로 가는 것으로 밝혀졌습니다. 로드할 항목이 없습니다. 그리고 "자신을 위해" 작동하는 증폭 단계가 필요한 사람은 누구입니까? 또한 입력 저항 값이 1kΩ에 불과하므로(각각 반전 증폭기 단의 입력 저항을 결정함) 이를 통해 흐르기 위해 지나치게 높은 전류가 필요하므로 신호 소스에 과부하가 걸립니다. 따라서 실제 회로에서 저항 Rin은 10kOhm 이상으로 선택되지만 주어진 이득에서 Rooc가 너무 높게 설정되지 않도록 100kOhm 이하도 바람직합니다. 이 값은 절대적이지 않지만 "첫 번째 근사치"에서 말했듯이 추정치만 가능합니다. 모두 특정 회로에 따라 다릅니다. 어쨌든 Rooc을 통해 흐르는 전류가 이 특정 연산 증폭기의 최대 출력 전류의 5 ... 10%를 초과하는 것은 바람직하지 않습니다.

합산된 신호는 비반전 입력에도 적용될 수 있습니다. 그것은 밝혀 비 반전 가산기. 원칙적으로 이러한 회로는 반전 가산기와 정확히 같은 방식으로 작동하며 출력은 입력 전압에 정비례하고 입력 저항 값에 반비례하는 신호가 됩니다. 그러나 실제로는 훨씬 덜 자주 사용됩니다. 고려해야 할 "갈퀴"가 포함되어 있습니다.

규칙 2는 "가상 제로 전위"가 있는 반전 입력에만 유효하므로 비반전 입력은 입력 전압의 대수적 합과 동일한 전위를 갖습니다. 따라서 입력 중 하나에서 사용할 수 있는 입력 전압은 다른 입력에 공급되는 전압에 영향을 줍니다. 비 반전 입력에는 "가상 잠재력"이 없습니다! 결과적으로 추가 회로 트릭을 적용해야 합니다.

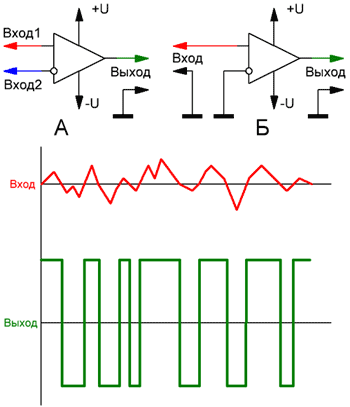

지금까지 OOS를 탑재한 OS 기반의 회로를 살펴보았다. 피드백이 완전히 제거되면 어떻게 됩니까? 이 경우 우리는 비교기(그림 14), 즉 입력에서 두 전위의 절대값을 비교하는 장치(영어 단어에서 비교하다- 비교하다). 출력에서 신호 중 어느 것이 다른 신호보다 큰지에 따라 공급 전압 중 하나에 접근하는 전압이 있습니다. 일반적으로 입력 신호는 입력 중 하나에 적용되고 다른 하나에는 비교되는 일정한 전압(소위 "기준 전압")이 적용됩니다. 제로 전위를 포함하여 무엇이든 될 수 있습니다(그림 14, B).

쌀. 14 비교기로 연산 증폭기를 켜는 방식

그러나 "덴마크 왕국"에서 모든 것이 그렇게 좋은 것은 아닙니다 ... 그리고 입력 사이의 전압이 0이면 어떻게됩니까? 이론상 출력도 0이어야 하지만 실제로는 - 절대. 입력 중 하나의 전위가 다른 것의 전위보다 약간 더 크다면, 이것은 이미 비교기의 입력에서 유도된 무작위 교란으로 인해 출력에서 혼돈 전압 서지가 발생하기에 충분할 것입니다.

실제로 모든 신호는 "노이즈"입니다. 이상은 정의할 수 없습니다. 그리고 입력의 전위가 같은 지점에 가까운 영역에서는 하나의 명확한 스위칭 대신 비교기의 출력에 출력 신호 버스트가 나타납니다. 이 현상을 방지하기 위해 비교기 회로가 종종 도입됩니다. 히스테리시스출력에서 비반전 입력으로 약한 양의 PIC를 생성합니다(그림 15).

쌀. 15 PIC로 인한 비교기의 히스테리시스 작동 원리

이 계획의 작동을 분석해 보겠습니다. 공급 전압은 ± 10V입니다(짝수 계정의 경우). 저항 Rin은 1kOhm이고 Rpos는 10kOhm입니다. 중간점 전위는 반전 입력에 적용되는 기준 전압으로 선택됩니다. 빨간색 곡선은 왼쪽 핀 Rin(입력 계획비교기), 파란색 - 연산 증폭기의 비 반전 입력에서의 전위 및 녹색 - 출력 신호.

입력 신호가 음의 극성을 갖는 동안 출력은 Rpos를 통해 해당 저항의 값에 반비례하여 입력 전압에 추가되는 음의 전압입니다. 결과적으로 음수 값의 전체 범위에서 비 반전 입력의 전위는 입력 신호 레벨보다 1V (절대 값) 더 높습니다. 비반전 입력의 전위가 반전 입력의 전위(입력 신호의 경우 +1V가 됨)와 같으면 연산 증폭기 출력의 전압이 음에서 전환되기 시작합니다 양극에. 비 반전 입력의 총 전위가 시작됩니다. 눈사태처럼그러한 전환의 과정을 지원하여 더욱 긍정적이 됩니다. 결과적으로 비교기는 입력 및 기준 신호의 중요하지 않은 잡음 변동을 단순히 "알지 못"합니다. 스위칭 시 비반전 입력에서 전위의 설명된 "단계"보다 진폭이 훨씬 더 작기 때문입니다. .

입력 신호가 감소하면 비교기 출력 신호의 역 스위칭이 -1V의 입력 전압에서 발생합니다. 입력 신호 레벨 간의 이러한 차이는 비교기 출력 스위칭으로 이어지는, 우리의 총 2V의 경우라고합니다. 히스테리시스. Rin에 대한 저항 Rpos가 클수록(POS 깊이가 작음) 스위칭 히스테리시스가 작아집니다. 따라서 Rpos \u003d 100kOhm에서는 0.2V에 불과하고 Rpos \u003d 1MΩ에서는 0.02V(20mV)가 됩니다. 히스테리시스(PIC 깊이)는 특정 회로에서 비교기의 실제 작동 조건을 기반으로 선택됩니다. 10mV가 많을 것이고 -와 2V가 작을 것입니다.

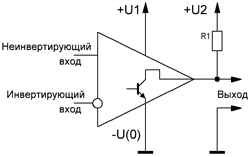

불행히도 모든 연산 증폭기를 비교기로 사용할 수 있는 것은 아닙니다. 아날로그와 디지털 신호 간의 매칭을 위해 특수 비교기 마이크로 회로가 생산됩니다. 그들 중 일부는 디지털 TTL 미세 회로(597CA2)에 연결하는 데 특화되어 있고 일부는 디지털 ESL 미세 회로(597CA1)에 연결하는 데 특화되어 있지만 대부분은 소위 말하는 것입니다. "일반용 비교기"(LM393/LM339/K554CA3/K597CA3). 연산 증폭기와의 주요 차이점은 오픈 컬렉터 트랜지스터에서 만들어진 출력단의 특수 장치에 있습니다(그림 16).

쌀. 16 일반 애플리케이션용 비교기 출력단

부하 저항에 대한 연결

이를 위해서는 외부 장치의 필수 사용이 필요합니다. 부하 저항(R1), 출력 신호가 단순히 물리적으로 높은(양의) 출력 레벨을 형성할 수 없습니다. 부하 저항이 연결된 전압 +U2는 비교기 칩 자체의 공급 전압 +U1과 다를 수 있습니다. 이것은 TTL 또는 CMOS와 같이 원하는 출력 레벨을 제공하는 간단한 수단을 허용합니다.

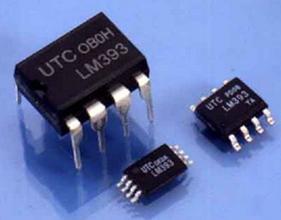

메모 대부분의 비교기에서 이중 LM393(LM193/LM293) 또는 회로에서 정확히 동일할 수 있는 대부분의 비교기에서 쿼드 LM339(LM139/LM239), 출력단 트랜지스터의 이미터는 음의 전원 단자에 연결되며, 이는 다소 범위를 제한합니다. 이와 관련하여 출력 트랜지스터의 컬렉터와 이미 터가 모두 별도로 출력되는 국내 521 / 554CA3의 아날로그 인 비교기 LM31 (LM111 / LM211)에주의를 기울이고 싶습니다. 비교기 자체의 공급 전압 이외의 다른 전압에 연결됩니다. 그것의 유일하고 상대적인 단점은 그것이 8핀(때로는 14핀) 패키지에 하나뿐이라는 것입니다. |

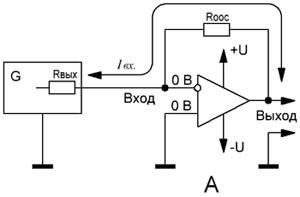

지금까지 입력 신호가 Rin을 통해 입력에 공급되는 회로를 고려했습니다. 그들은 모두였다 변환기입력 전압휴일 전압같은. 이 경우 입력 전류는 Rin을 통해 흐릅니다. 저항을 0으로 하면 어떻게 될까요? 회로는 위에서 논의한 반전 증폭기와 정확히 동일한 방식으로 작동하며 신호 소스(Rout)의 출력 임피던스만 Rin 역할을 하며 다음을 얻습니다. 변환기입력 현재의 안에휴일 전압(그림 17).

쌀. 17 연산 증폭기의 전류-전압 변환기 구성표

반전 입력의 전위는 반전되지 않은 것과 동일하기 때문에(이 경우 "가상 영점"), 전체 입력 전류( 나안에)는 신호 소스(G)의 출력과 연산 증폭기의 출력 사이에서 Rooc을 통해 흐를 것입니다. 이러한 회로의 입력 저항은 0에 가깝기 때문에 측정된 회로를 통해 흐르는 전류에 실질적으로 영향을 미치지 않는 마이크로/밀리암미터를 기반으로 구축할 수 있습니다. 아마도 유일한 제한 사항은 초과해서는 안되는 연산 증폭기의 허용 입력 전압 범위일 것입니다. 예를 들어 선형 포토다이오드 전류-전압 변환기 및 기타 여러 회로를 구축하는 데 사용할 수도 있습니다.

우리는 에서 OS 기능의 기본 원리를 조사했습니다. 다양한 계획그것의 포함. 한 가지 중요한 질문이 남아 있습니다. 음식.

위에서 언급했듯이 연산 증폭기에는 일반적으로 입력 2개, 출력 2개, 전원 핀 2개(양수 및 음수)의 5개 핀만 있습니다. 에 일반적인 경우바이폴라 전원이 사용됩니다. 즉, 전원 공급 장치에는 전위가 있는 3개의 출력이 있습니다. + U; 0; -유.

다시 한 번 위의 모든 수치를 주의 깊게 고려하고 연산 증폭기에서 중간점의 별도 출력이 아니 ! 내부 회로가 작동하는 데 단순히 필요하지 않습니다. 일부 회로에서는 비반전 입력이 중간점에 연결되었지만 이것은 규칙이 아닙니다.

따라서, 압도적 다수 최신 연산 증폭기는 전력을 공급하도록 설계되었습니다. 유니폴라 전압! 논리적인 질문이 생깁니다. 그림에서 그렇게 완고하게 그리고 부러워하는 불변으로 묘사했다면 "왜 양극성 전원이 필요합니까?"

그것은 단지 아주 편안하게다음과 같은 이유로 실용적인 목적을 위해:

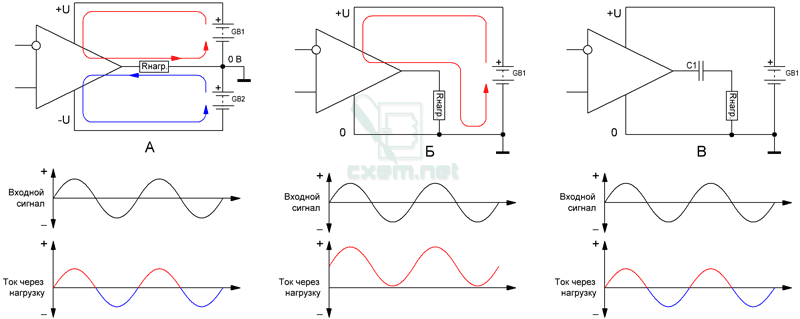

A) 부하를 통한 충분한 전류 및 출력 전압 스윙을 보장하기 위해(그림 18).

쌀. 18 연산 증폭기를 공급하기 위한 다양한 옵션이 있는 부하를 통한 출력 전류의 흐름

지금은 그림에 표시된 회로("블랙박스")의 입력(및 OOS) 회로를 고려하지 않습니다. 일부 입력 정현파 신호가 입력(그래프의 검은 정현파)에 적용되고 출력이 동일한 정현파 신호이며 그래프의 입력 컬러 정현파에 대해 증폭된 것으로 간주하겠습니다.

부하 Rload를 연결할 때. 연산 증폭기의 출력과 전원 공급 장치(GB1 및 GB2) 연결의 중간 지점 사이 - 그림. 도 18, A에서 전류는 중간점(각각 적색 및 청색 반파)을 중심으로 대칭적으로 부하를 통해 흐르고 그 진폭은 최대이고 Rload에서의 전압 진폭이다. 또한 가능한 최대 - 거의 공급 전압에 도달할 수 있습니다. 해당 극성의 전원에서 나오는 전류는 OS, Rload를 통해 닫힙니다. 및 전원(각 방향의 전류 흐름을 나타내는 빨간색 및 파란색 선).

연산 증폭기 전원 공급 장치의 내부 저항이 매우 낮기 때문에 부하를 통과하는 전류는 저항과 연산 증폭기의 최대 출력 전류(일반적으로 25mA)에 의해서만 제한됩니다.

연산 증폭기가 다음과 같이 단극 전압에 의해 전원이 공급될 때 일반 버스전원의 음극 (음극)은 일반적으로 부하의 두 번째 출력이 연결되는 것으로 선택됩니다 (그림 18, B). 이제 부하를 통과하는 전류는 한 방향(빨간색 선으로 표시)으로만 흐를 수 있으며 두 번째 방향은 단순히 아무데도 흐를 수 없습니다. 즉, 부하를 통과하는 전류가 비대칭(맥동)이 됩니다.

이 옵션이 나쁘다고 분명히 말할 수는 없습니다. 부하가 예를 들어 동적 헤드인 경우 분명히 나쁜 것입니다. 그러나 연산 증폭기의 출력과 전원 레일 중 하나(일반적으로 음의 극성) 사이에 부하를 연결하는 것이 허용될 뿐만 아니라 유일하게 가능한 애플리케이션이 많이 있습니다.

그럼에도 불구하고 단극 전원으로 부하를 통과하는 전류 흐름의 대칭을 보장해야 하는 경우 갈바닉 커패시터 C1을 사용하여 연산 증폭기의 출력에서 이를 갈바닉 분리해야 합니다(그림 18, B ).

B) 반전 입력의 요구되는 전류를 보장하기 위해 뿐만 아니라 바인딩일부에 신호를 입력 임의로 선택된수준 수락기준 (영) - 직류에 대한 OS의 작동 모드 설정 (그림 19).

쌀. 19 연산 증폭기 공급을 위한 다양한 옵션으로 입력 신호 소스 연결

이제 부하 연결을 고려하지 않고 입력 신호 소스를 연결하는 옵션을 고려하십시오.

반전 및 비 반전 입력을 전원 공급 장치 연결의 중간 지점에 연결하는 것이 이전에 제공된 다이어그램을 분석할 때 고려되었습니다(그림 19, A). 비 반전 입력이 전류를 소비하지 않고 단순히 중간 전위를 받아들이면 직렬로 연결된 신호 소스(G)와 Rin을 통해 전류가 흐르고 해당 전원을 통해 닫힙니다! 그리고 내부 저항은 입력 전류(Rin보다 수십 배 더 작음)에 비해 무시할 수 있기 때문에 실제로 공급 전압에 영향을 미치지 않습니다.

따라서 연산 증폭기의 단극 공급 장치를 사용하면 R1R2 분배기를 사용하여 비반전 입력에 공급되는 전위를 아주 쉽게 형성할 수 있습니다(그림 19, B, C). 이 분배기의 일반적인 저항 값은 10 ... 100 kOhm이며 효과를 크게 줄이기 위해 10 ... 22 마이크로 패러드 커패시터로 더 낮은 것을 션트하는 것이 매우 바람직합니다(공통 네거티브 버스에 연결됨) 이러한 전위에 대한 공급 전압 리플의 인공의 중간점.

그러나 동일한 입력 전류 때문에 신호 소스(G)를 이 인공 중간점에 연결하는 것은 매우 바람직하지 않습니다. 추측해 봅시다. 분배기 R1R2 = 10kOhm 및 Rin = 10… 100kOhm의 정격에서도 입력 전류는 나안에기껏해야 1/10, 최악의 경우 분배기를 통과하는 전류의 최대 100%입니다. 결과적으로 비반전 입력의 전위는 입력 신호와 결합하여(동위상) 동일한 양만큼 "부동"합니다.

이러한 연결로 DC 신호를 증폭할 때 서로에 대한 입력의 상호 영향을 제거하려면 저항 R3R4(그림 19, B)로 형성된 신호 소스에 대해 인공 중간점의 별도 전위를 구성해야 합니다. 신호가 증폭된다 교류, 커패시터 C2를 사용하여 반전 입력에서 신호 소스를 전기적으로 분리합니다(그림 19, B).

위의 다이어그램(그림 18, 19)에서 우리는 기본적으로 출력 신호가 전원 공급 장치의 중간점이나 인위적인 중간점에 대해 대칭이어야 한다고 가정했습니다. 실제로 이것이 항상 필요한 것은 아닙니다. 종종 출력 신호가 주로 양극 또는 음극을 갖기를 원합니다. 따라서 전원 공급 장치의 양극과 음극이 절대값이 같을 필요는 전혀 없습니다. 그 중 하나는 OS의 정상적인 기능을 보장하는 방식으로만 다른 것보다 절대 값이 훨씬 작을 수 있습니다.

논리적인 질문이 생깁니다. "정확히 어느 것이요?" 이에 대한 답으로 연산증폭기의 입출력 신호의 허용 전압 범위를 간단히 살펴보자.

모든 연산 증폭기의 경우 출력 전위는 양극 전원 레일의 전위보다 높고 음극 전원 레일의 전위보다 낮을 수 없습니다. 즉, 출력 전압은 공급 전압의 한계를 넘을 수 없습니다. 예를 들어 OPA277 연산 증폭기의 경우 10kΩ의 부하 저항에서 출력 전압은 양의 전원 레일보다 2V 낮고 음의 전원 레일보다 0.5V 낮습니다. 출력 전압의 이러한 "데드 존"의 너비는 연산 증폭기 출력이 도달할 수 없는 값은 출력단 회로, 부하 저항 등과 같은 직렬 요소에 따라 달라집니다. 데드존이 최소인 연산 증폭기가 있습니다. 예를 들어 부하 10kΩ에서 공급 레일 전압에 대해 50mV(OPA340의 경우), 이 연산 증폭기의 기능을 "레일 투 레일"(R2R)이라고 합니다.

반면에 범용 연산 증폭기의 경우 입력 신호도 공급 전압을 초과해서는 안 되며 일부의 경우 1.5 ... 2V 미만이어야 합니다. 그러나 특정 입력 스테이지 회로가 있는 연산 증폭기가 있습니다. (예를 들어, 동일한 LM358 / LM324) , 음의 전력 수준에서뿐만 아니라 0.3V의 "음"에서도 작동 할 수 있으므로 공통 음의 버스가있는 단극 전원 공급 장치와 함께 사용하는 것이 크게 용이합니다.

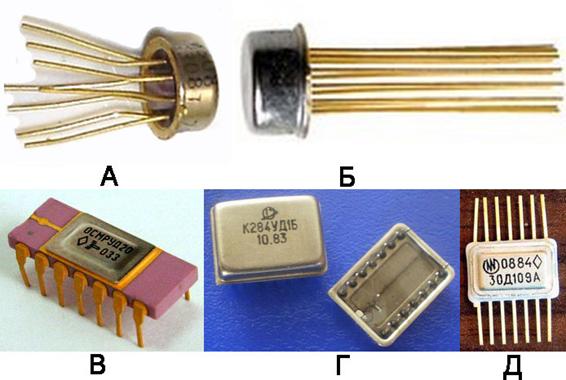

마지막으로 이 "거미 벌레"를 보고 느껴봅시다. 냄새를 맡고 핥을 수도 있습니다. 난 인정해. 초보 라디오 아마추어가 사용할 수 있는 가장 일반적인 옵션을 고려하십시오. 특히 오래된 장비에서 연산 증폭기를 납땜해야 하는 경우.

오래된 디자인의 연산 증폭기의 경우 틀림없이자기 여기를 방지하기 위해 주파수 보정을 위해 외부 회로가 필요하고 추가 결론이 존재하는 것이 특징적이었습니다. 이 때문에 일부 연산 증폭기는 8핀 패키지(그림 20, A)에 "맞지"도 않았고 12핀 원형 금속 유리로 만들어졌습니다(예: K140UD1, K140UD2, K140UD5)(그림 20 , B) 또는 14핀 DIP 패키지(예: K140UD20, K157UD2)(그림 20, B). 약어 DIP는 영어 표현 "Dual In line Package"의 약어로 "양면 패키지"로 번역됩니다.

둥근 금속 유리 케이스(그림 20, A, B)는 70년대 중반까지 수입 연산 증폭기의 주요 케이스로, 80년대 중반까지 국내 연산 증폭기의 주요 케이스로 사용되었으며 현재는 소위. "군사" 신청서("5차 승인").

때로는 국내 연산 증폭기가 현재 다소 "이국적인"케이스에 배치되었습니다. 하이브리드 K284UD1의 15핀 직사각형 금속 유리(그림 20, D)는 키가 케이스에서 추가로 15번째 핀이고 기타 . 사실, 나는 개인적으로 연산 증폭기를 배치하기 위한 평면 14핀 패키지(그림 20, E)를 만나지 못했습니다. 그들은 디지털 회로에 사용되었습니다.

쌀. 국내 연산증폭기 20건

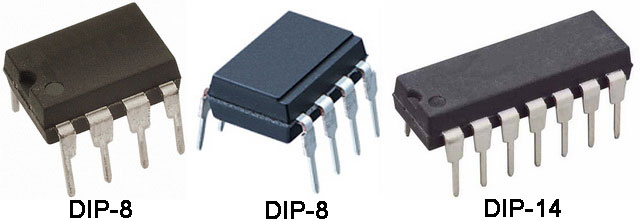

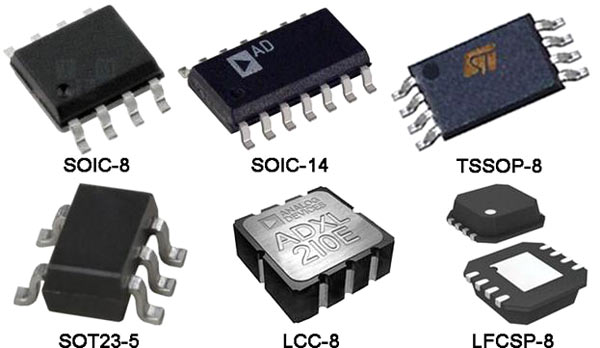

최신 연산 증폭기는 대부분 칩에 바로 수정 회로를 포함하므로 최소 핀 수(예: 단일 연산 증폭기용 5핀 SOT23-5 - 그림 1)로 처리할 수 있습니다. 23). 이를 통해 하나의 케이스에 단일 칩으로 만들어진 2~4개의 완전히 독립적인(공통 전원 출력 제외) 연산 증폭기를 배치할 수 있습니다.

쌀. 21 출력 실장용 최신 연산 증폭기의 2열 플라스틱 케이스(DIP)

때때로 단일 행 8핀(그림 22) 또는 9핀 패키지(SIP) - K1005UD1에 배치된 연산 증폭기를 찾을 수 있습니다. 약어 SIP는 영어 표현 "Single In line Package"의 약어로 "단방향 핀아웃이 있는 하우징"으로 번역됩니다.

쌀. 22 관통 구멍 장착용 이중 연산 증폭기의 단일 행 플라스틱 케이스(SIP-8)

그들은 보드에서 차지하는 공간을 최소화하도록 설계되었지만 불행히도 "늦었다". 이때까지 표면 실장 패키지(SMD - 표면 실장 장치)는 보드 트랙에 직접 납땜하여 널리 보급되었습니다(그림 23). ). 그러나 초보자에게는 사용에 상당한 어려움이 있습니다.

쌀. 표면 실장용 최신 수입 연산 증폭기 23개(SMD)

매우 자주 동일한 미세 회로가 제조업체에서 다른 패키지로 "포장"될 수 있습니다(그림 24).

쌀. 24개의 다른 패키지에 있는 동일한 칩에 대한 배치 옵션

모든 미세 회로의 결론에는 소위 순차 번호가 매겨집니다. "key"는 1번의 출력 위치를 나타냅니다(그림 25). 에 어느 본체가 터미널과 함께 위치하는 경우 푸시, 번호가 오름차순으로 지정됩니다. 에 맞서 시계 방향으로!

쌀. 연산 증폭기의 25핀 할당

다양한 경우(핀아웃), 평면도;

화살표로 표시된 번호 매기기 방향

둥근 금속 유리 케이스에서 키는 측면 돌출 형태를 갖습니다(그림 25, A, B). 여기이 키의 위치에서 거대한 "갈퀴"가 가능합니다! 국내 8핀 케이스(302.8)에서 키는 첫 번째 핀(그림 25, A) 맞은편에 있고 수입 TO-5에서는 8번째 핀(그림 25, B) 맞은편에 있습니다. 12핀 케이스의 경우 국내(302.12) 및 수입품 모두 키가 있습니다. ~ 사이첫 번째와 열두 번째 결론.

일반적으로 원형 유리 금속 및 DIP 패키지의 반전 입력은 2번째 핀에, 비반전 입력은 3번째 핀에, 출력은 6번째 핀에, 마이너스 전력은 4번째 핀에, 핀 4. 7에 전원 플러스. 그러나 OU K140UD8, K574UD1의 핀아웃에는 예외가 있습니다(또 다른 가능한 "갈퀴"!). 그들에서 결론의 번호 매기기는 대부분의 다른 유형에 일반적으로 허용되는 것과 비교하여 시계 반대 방향으로 1만큼 이동합니다. 그들은 수입 케이스 (그림 25, B)와 같이 터미널에 연결되며 번호는 국내 케이스에 해당합니다 (그림 25, A).

에 지난 몇 년 OS "가정용"의 대부분은 플라스틱 케이스에 넣기 시작했습니다(그림 21, 25, C-D). 이 경우 키는 첫 번째 핀 반대편의 오목한 부분(점)이거나 첫 번째 핀과 8번째(DIP-8) 또는 14번째(DIP-14) 핀 사이의 케이스 끝에 있는 컷아웃이거나 핀의 전반부(그림 21, 중간). 이 경우 핀 번호도 적용됩니다. 에 맞서 시계 방향으로위에서 보았을 때(결론은 당신에게서 멀어짐).

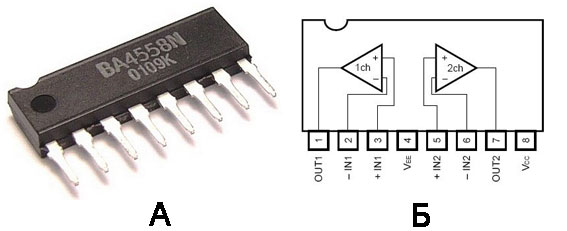

위에서 언급했듯이 내부적으로 수정된 연산 증폭기에는 총 5개의 출력이 있으며 그 중 3개(2개의 입력 및 1개의 출력)만 각 개별 연산 증폭기에 속합니다. 이것은 하나의 8핀 패키지(그림 25, D)의 하나의 칩에 완전히 독립적인 두 개의 연산 증폭기(2개의 핀이 더 필요한 플러스 및 마이너스 전력 제외), 14개 패키지에 4개까지 배치할 수 있게 했습니다. -핀 패키지(그림 25, D). 결과적으로 현재 대부분의 연산 증폭기는 TL062, TL072, TL082, 저렴하고 간단한 LM358 등과 같이 적어도 듀얼로 생산됩니다. 내부 구조는 정확히 동일하지만 쿼드 - 각각 TL064, TL074, TL084 및 LM324.

LM324(K1401UD2)의 국내 아날로그와 관련하여 "레이크"가 하나 더 있습니다. LM324에서 전원 공급 장치의 플러스가 4번째 핀에 연결되고 마이너스가 11번째 핀에 연결되면 K1401UD2에는 다음과 같습니다. 반대의 경우: 전원의 플러스는 11번째 핀으로, 마이너스는 4번째 핀으로 가져옵니다. 그러나 이 차이로 인해 배선에 문제가 발생하지는 않습니다. 연산 증폭기 핀의 핀 배치가 완전히 대칭이기 때문에(그림 25, E) 첫 번째 핀이 여덟 번째 핀을 대신하도록 케이스를 180도 돌리면 됩니다. 네, 그게 전부입니다.

가져온 OU(OU뿐만 아니라)의 레이블 지정에 대한 몇 마디. 처음 300개의 디지털 지정이 개발된 경우 디지털 코드의 첫 번째 숫자로 품질 그룹을 지정하는 것이 일반적이었습니다. 예를 들어 LM158/LM258/LM358 연산 증폭기, LM193/LM293/LM393 비교기, TL117/TL217/TL317 조정 가능한 3핀 안정기 등은 내부 구조가 완전히 동일하지만 작동 온도 범위가 다릅니다. LM158(TL117)의 경우 작동 온도 범위는 섭씨 영하 55 ~ +125 ... 150도(소위 "전투" 또는 군사 범위)이고 LM258(TL217)의 경우 - 40 ~ +85도(" 산업용" 범위) 및 LM358(TL317)의 경우 - 0 ~ +70도("가정용" 범위). 동시에, 그 가격은 그러한 그라데이션에 완전히 부적절하거나 매우 약간 다를 수 있습니다 ( 불가사의한 가격 책정 방식!). 따라서 첫 번째 "트로이카"를 특별히 쫓지 않고 초보자의 "주머니용"으로 사용할 수 있는 모든 표시로 구입할 수 있습니다.

처음 300개의 디지털 표시가 소진된 후 신뢰성 그룹은 문자로 표시되기 시작했으며 그 의미는 이러한 구성 요소에 대한 데이터시트(데이터시트는 문자 그대로 "데이터 테이블"로 번역됨)에서 해독됩니다.

결론

그래서 우리는 연산 증폭기 작동의 "알파벳"을 연구하여 약간과 비교기를 캡처했습니다. 다음으로 이 "문자"에서 단어, 문장 및 의미 있는 전체 "구성"(실행 가능한 구성표)을 추가하는 방법을 배워야 합니다.

유감스럽게도 "광대함을 파악하는 것은 불가능합니다." 이 기사에 제시된 자료가 이러한 "블랙 박스"가 작동하는 방식을 이해하는 데 도움이 되었다면 입력, 출력 및 과도 특성의 영향인 "스터핑"에 대한 분석을 더욱 심화하는 것이 고급 연구의 과제입니다. 이에 대한 정보는 다양한 기존 문헌에 상세하고 철저하게 설명되어 있습니다. 오컴의 할아버지 윌리엄은 다음과 같이 말하곤 했습니다. 이미 잘 설명한 내용을 반복할 필요가 없습니다. 게으르지 않고 읽기만 하면 됩니다.

11. http://www.texnic.ru/tools/lekcii/electronika/l6/lek_6.html

따라서 저자를 존경하는 등의 마음으로 이만 물러나겠습니다. 알렉세이 소콜류크 ()

비 반전 증폭기는 반전 증폭기 및 전압 팔로워 회로와 함께 아날로그 전자 제품의 가장 기본적인 세 가지 회로 중 하나일 것입니다. 회로가 작동하기 위해 바이폴라 전원이 필요하지 않기 때문에 반전 증폭기보다 훨씬 간단합니다.

공식에 포함된 단위에 주의하십시오. 이것은 비 반전 증폭기가 항상 1보다 큰 이득을 갖는다는 것을 말하며, 이는 그러한 회로를 사용하면 신호를 감쇠할 수 없음을 의미합니다.

비 반전 증폭기가 어떻게 작동하는지 더 잘 이해하기 위해 회로를보고 출력에서 전압이 무엇인지 생각해 봅시다.

가장 먼저 생각해야 할 것은 연산 증폭기의 두 입력에 어떤 전압이 존재하는지입니다. 연산 증폭기의 작동을 설명하는 첫 번째 규칙을 상기하십시오.

규칙 번호 1 - 연산 증폭기는 NOS(음의 피드백)를 통해 입력에 출력을 가하여 반전(-) 및 비반전(+) 입력 모두의 전압이 동일해집니다.

즉, 반전 입력의 전압은 3V입니다. 다음 단계에서는 10k 저항을 고려해 보겠습니다. 우리는 전압과 저항을 알고 있습니다. 즉, 이를 통해 흐르는 전류를 계산할 수 있습니다.

I \u003d U / R \u003d 3V / 10k \u003d 300μA.

이 전류는 규칙 2에 따라 반전 입력(-)에서 가져올 수 없으므로 증폭기의 출력에서 나옵니다.

규칙 #2 - 증폭기 입력은 전류를 끌어오지 않는다

300µA의 전류도 20k 저항을 통해 흐릅니다. 옴의 법칙을 사용하여 전압을 쉽게 계산할 수 있습니다.

U = IR = 300uA * 20k = 6V

이 전압이 증폭기의 출력 전압이라는 것이 밝혀졌습니다. 아니, 그렇지 않다. 20k 저항은 단자 중 하나에서 3V의 전압을 갖는다는 것을 기억하십시오. 두 저항의 전압이 어떻게 향하는지 확인하십시오.

전류는 화살표 방향과 반대 방향으로 흐르며 더 많은 점을 상징합니다. 높은 전압. 따라서 계산된 6V에 입력에 3V를 더 추가해야 합니다. 이 경우 최종 결과는 9V가 됩니다.

저항 R1과 R2가 간단한 것을 형성한다는 점은 주목할 가치가 있습니다. 분배기의 개별 저항을 가로지르는 전압의 합은 분배기에 공급되는 전압과 같아야 합니다. 전압은 흔적 없이 사라지고 아무데도 나타나지 않을 수 있습니다.

마지막으로 마지막 규칙으로 결과를 확인해야 합니다.

규칙 번호 3 - 입력 및 출력의 전압은 연산 증폭기의 양과 음 공급 전압 사이의 범위에 있어야 합니다.

즉, 우리가 계산한 전압이 현실적으로 얻어질 수 있는지 확인이 필요하다. 종종 초보자는 증폭기가 "Perpetuum Mobile"처럼 작동하고 무에서 전압을 생성한다고 생각합니다. 그러나 증폭기가 작동하려면 전력도 필요하다는 것을 기억해야 합니다.

클래식 증폭기는 -15V 및 +15V의 전압에서 작동합니다. 이러한 상황에서 9V는 공급 전압 범위에 있으므로 계산된 9V가 실제 전압입니다. 그러나 최신 증폭기는 종종 5V 이하에서 작동합니다. 이러한 상황에서 증폭기가 9V를 출력할 가능성은 없습니다.

따라서 회로를 설계할 때 항상 이론적 계산을 구성 요소의 실제 및 물리적 기능과 비교하여 확인해야 한다는 점을 기억해야 합니다.